Product Summary

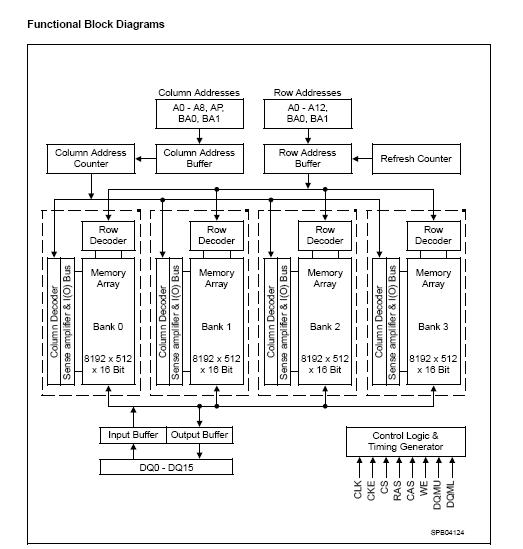

The HYB39L256160AC-7.5 is a 256 MBit Synchronous Low-Power DRAM. It is organized as 4 banks × 4Mbit × 16. The HYB39L256160AC-7.5 achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock. Auto Refresh (CBR) and Self Refresh operation are supported. The HYB39L256160AC-7.5 operates with a single 3.3V ± 0.3V power supply.

Parametrics

HYB39L256160AC-7.5 absolute maximum ratings: (1)Operating Case Temperature Range (commercial): 0 to +70℃; (2)Storage Temperature Range: –55 to +150℃; (3)Input/Output Voltage VIN, VOUT: –1.0 to VDD + 0.5V; (4) Input/Output Voltage VIN, VOUT: –1.0 to +4.6V; (5) Power Supply Voltages VDD, VDDQ: –1.0 to +4.6V; (6) Power Dissipation: 0.7W; (7) Data out Current (short circuit): 50mA.

Features

HYB39L256160AC-7.5 features: (1)16Mbit × 16 organisation; (2)VDD = VDDQ = 3.3 V; (3)Fully Synchronous to Positive Clock Edge; (4)Four Banks controlled by BA0 & BA1; (5)Programmable CAS Latency: 2, 3; (6)Programmable Wrap Sequence: Sequential or Interleave; (7)Automatic and Controlled Precharge Command; (8)Programmable Burst Length: 1, 2, 4, 8 and full page; (9)Data Mask for byte control; (10)Auto Refresh (CBR); (11)8192 Refresh Cycles / 64ms; (12)Very low Self Refresh current; (13)Power Down and Clock Suspend Mode; (14)Random Column Address every CLK(1-N Rule).

Diagrams

|

HYB3116165BST-60 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB3116405BJ/BT(L)-50 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB3116405BJ/BT(L)-60 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB3116405BJ/BT(L)-70 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB3117405BJ/BT(L)-50 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB3117405BJ/BT(L)-60 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))