Product Summary

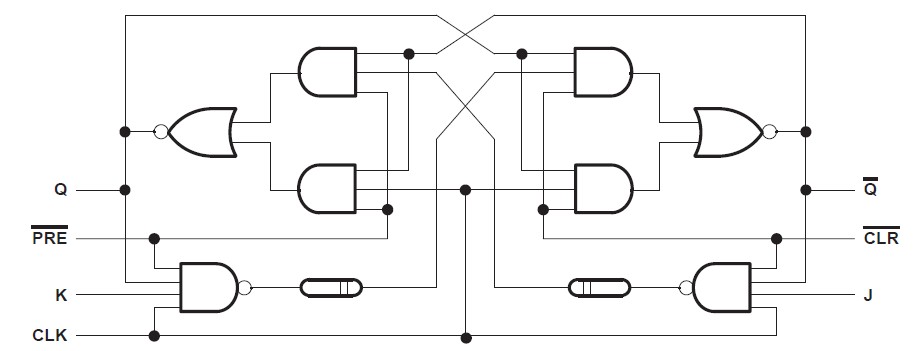

The SN74ALS112ADR is a dual j-k negative-edge-triggered flip-flop with clear and preset. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR of the SN74ALS112ADR are inactive (high), data at the J and K inputs meeting the setup-time requirements is transferred to the outputs on the negative-going edge of the clock pulse (CLK). Clock triggering occurs at a voltage level and is not directly related to the fall time of the clock pulse. The SN74ALS112ADR is characterized for operation from 0℃ to 70℃.

Parametrics

SN74ALS112ADR absolute maximum ratings: (1)Supply voltage, VCC: 7 V; (2)Input voltage, VI: 7 V; (3)Operating free-air temperature range, TA: 0℃ to 70℃; (4)Storage temperature range: –65℃ to 150℃.

Features

SN74ALS112ADR features: (1)Fully Buffered to Offer Maximum Isolation From External Disturbance; (2)Package Options Include Plastic Small-Outline (D) Packages, Ceramic Chip Carriers (FK), and Standard Plastic (N) and Ceramic (J) 300-mil DIPs.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

SN74ALS112ADR |

Texas Instruments |

Flip Flops Dual Neg-Edge-Trig J-K Flip-Flop |

Data Sheet |

|

|

||||||||||||

|

SN74ALS112ADRE4 |

Texas Instruments |

Flip Flops Dual Neg-Edge-Trig J-K Flip-Flop |

Data Sheet |

|

|

||||||||||||

|

SN74ALS112ADRG4 |

Texas Instruments |

Flip Flops Dual J-K Neg Edge TRIGRD Flip Flops |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))