Product Summary

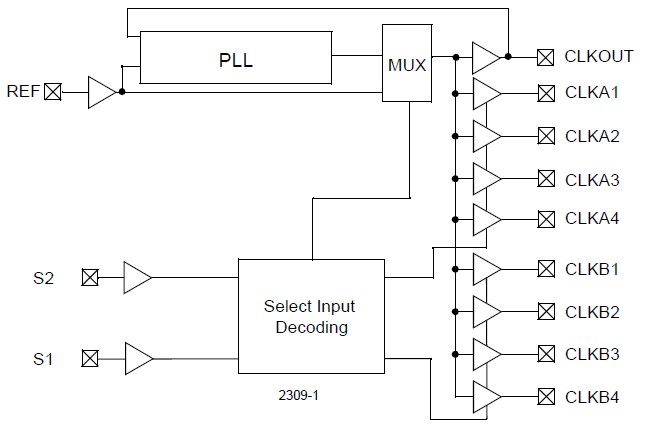

The CY2309SI-1HT is a low-cost 3.3V zero delay buffer designed to distribute high-speed clocks and is available in a 16-pin SOIC or TSSOP package. The CY2309SI-1HT accepts one reference input, and drives out five low-skew clocks. The -1H versions of each device operate at up to 100-/133-MHz frequencies, and have higher drive than the -1 devices. The CY2309SI-1HT has two banks of four outputs each, which can be controlled by the Select inputs.

Parametrics

CY2309SI-1HT absolute maxing ratings: (1)Supply Voltage to Ground Potential: –0.5V to +7.0V; (2)DC Input Voltage (Except REF): –0.5V to VDD + 0.5V; (3)DC Input Voltage REF: –0.5V to 7V; (4)Storage Temperature: –65℃ to +150℃; (5)Junction Temperature: 150℃; (6)Static Discharge Voltage(per MIL-STD-883, Method 3015): > 2,000V.

Features

CY2309SI-1HT features: (1)10-MHz to 100-/133-MHz operating range, compatible with CPU and PCI bus frequencies; (2)Zero input-output propagation delay ; (3)Multiple low-skew outputs; (4)Less than 200 ps cycle-cycle jitter, compatible with Pentium-based systems; (5)Test Mode to bypass phase-locked loop (PLL); (6)Available in space-saving 16-pin 150-mil SOIC or 4.4-mm TSSOP packages; (7)3.3V operation; (8)Industrial temperature available.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY2309SI-1HT |

Cypress Semiconductor |

Phase Locked Loops (PLL) 3. 3V ZDB Internal Feedck |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

CY2300 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY2300SXC |

Cypress Semiconductor |

Phase Locked Loops (PLL) 3.3VZDB COM |

Data Sheet |

|

|

||||||||||||

|

CY2300SXCT |

Cypress Semiconductor |

Phase Locked Loops (PLL) 3.3VZDB COM |

Data Sheet |

|

|

||||||||||||

|

CY2302 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY23020-1 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY23020LFI-3 |

Cypress Semiconductor |

Phase Locked Loops (PLL) 400MHz IND Zero Delay Buffer |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))