Product Summary

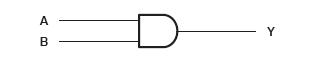

The SN74LV08ADBR is a quadruple 2-input positive-and gate. It is designed for 2-V to 5.5-V VCC operation. The SN74LV08ADBR performs the Boolean function Y=A×B or Y=A+B in positive logic. The SN74LV08ADBR is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down.

Parametrics

SN74LV08ADBR absolute maximum ratings: (1)Supply voltage range, VCC: -0.5 V to 7 V; (2)Input voltage range, VI: -0.5 V to 7 V; (3)Voltage range applied to any output in the high-impedance; (4)or power-off state, VO: -0.5 V to 7 V; (5)Output voltage range, VO: -0.5 V to VCC+0.5V; (6)Input clamp current, IIK (VI<0): -20mA; (7)Output clamp current, IOK (VO<0): -50mA; (8)Continuous output current, IO (VO=0 to VCC): ±25mA; (9)Continuous current through VCC or GND: ±50mA; (10)Package thermal impedance, θJA: 96℃/W; (11)Storage temperature range, Tstg: 65℃ to 150℃.

Features

SN74LV08ADBR features: (1)2-V to 5.5-V VCC Operation; (2)Max tpd of 7 ns at 5 V; (3)Typical VOLP (Output Ground Bounce)<0.8V at VCC=3.3V, TA=25℃; (4)Typical VOHV (Output VOH Undershoot)>2.3V at VCC=3.3V, TA=25℃; (5)Support Mixed-Mode Voltage Operation on All Ports; (6)Ioff Supports Partial-Power-Down Mode Operation; (7)Latch-Up Performance Exceeds 250mA Per JESD 17; (8)ESD Protection Exceeds JESD 22: 2000-V Human-Body Model (A114-A), 200-V Machine Model (A115-A), 1000-V Charged-Device Model (C101).

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

SN74LV08ADBR |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quad 2-Input |

Data Sheet |

|

|

||||||||||||

|

SN74LV08ADBRE4 |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quadruple 2-Input Positive-AND Gates |

Data Sheet |

|

|

||||||||||||

|

SN74LV08ADBRG4 |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quad 2 Input Pos AND Gates |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))