Product Summary

The CDCV855IPWR is a 2.5V phase-lock loop clock driver. When PWRDWN is high, the outputs switch in phase and frequency with CLK. When PWRDWN is low, all outputs are disabled to a high-impedance state (3-state), and the PLL is shut down (low-power mode). The CDCV855IPWR also enters this low-power mode when the input frequency falls below a suggested detection frequency that is below 20 MHz (typical 10 MHz).

Parametrics

CDCV855IPWR absolute maxing ratings: (1)Supply voltage range, VDDQ, AVDD: -0.5 V to 3.6 V; (2)Input voltage range, VI: -0.5 V to VDDQ + 0.5 V; (3)Output voltage range, VO: -0.5 V to VDDQ + 0.5 V; (4)Input clamp current, IIK (VI < 0 or VI > VDDQ): ±50 mA; (5)Output clamp current, IOK (VO < 0 or VO > VDDQ): ±50 mA; (6)Continuous output current, IO (VO = 0 to VDDQ): ±50 mA; (7)Continuous current to GND or VDDQ: ±100 mA; (8)Package thermal impedance, θJA: PW package: 105.8℃/W; (9)Storage temperature range Tstg: -65℃ to 150℃.

Features

CDCV855IPWR features: (1)Phase-Lock Loop Clock Driver for Double Data-Rate Synchronous DRAM Applications; (2)Spread Spectrum Clock Compatible; (3)Operating Frequency: 60 MHz to 180 MHz; (4)Low Jitter (cyc–cyc): ±50 ps; (5)Distributes One Differential Clock Input to Four Differential Clock Outputs; (6)Enters Low Power Mode and Three-State Outputs When Input CLK Signal Is Less Than 20 MHz or PWRDWN Is Low; (7)Operates From Dual 2.5-V Supplies.

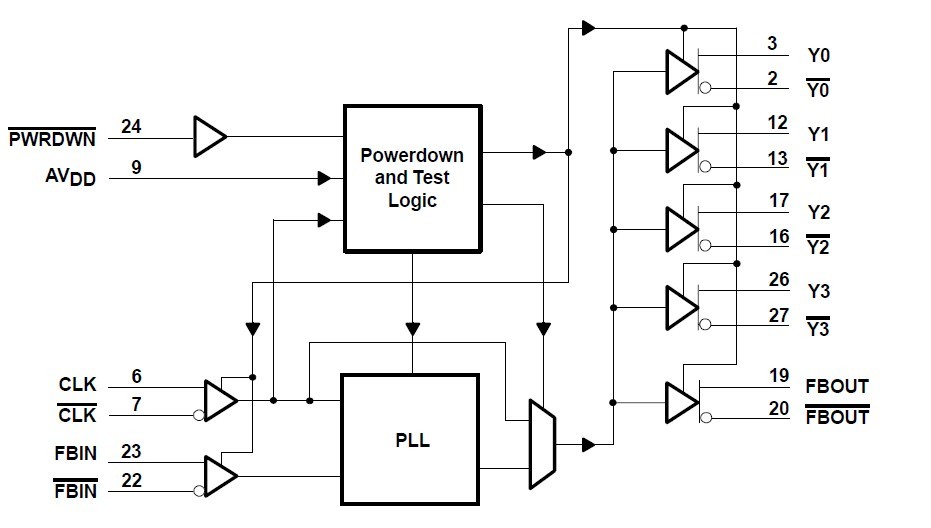

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CDCV855IPWR |

Texas Instruments |

Clock Drivers & Distribution 1:4 DDR PLL CLOCK DRIVERS |

Data Sheet |

|

|

||||||||||

|

CDCV855IPWRG4 |

Texas Instruments |

Clock Drivers & Distribution 1:4 DDR PLL CLOCK DRIVERS |

Data Sheet |

|

|

||||||||||

(China (Mainland))

(China (Mainland))