Product Summary

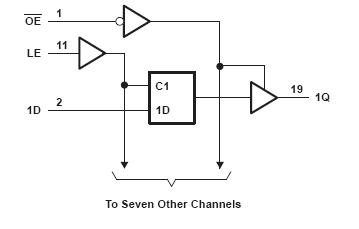

The 74LVT573DWR is a 3.3-V ABT octal transparent D-type latch with 3-state outputs. The 74LVT573DWR is designed specifically for low-voltage (3.3-V) VCC operation, but with the capability to provide a TTL interface to a 5-V system environment. The eight latches of the 74LVT573DWR are transparent D-type latches. While the latch-enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the logic levels set up at the D inputs.

Parametrics

74LVT573DWR absolute maximum ratings: (1)Supply voltage range, VCC: –0.5 V to 4.6 V; (2)Input voltage range, VI: –0.5 V to 7 V; (3)Voltage range applied to any output in the high state or power-off state, VO: –0.5 V to 7 V; (4)Current into any output in the low state, IO: 128 mA; (5)Current into any output in the high state, IO: 64 mA; (6)Input clamp current, IIK (VI<0): –50 mA; (7)Output clamp current, IOK (VO<0): –50 mA; (8)Maximum power dissipation at TA = 55℃ (in still air): DB package: 0.6 W, DW package: 1.6 W, PW package: 0.7 W; (9)Storage temperature range, Tstg: –65℃ to 150℃.

Features

74LVT573DWR features: (1)State-of-the-Art Advanced BiCMOS Technology (ABT) Design for 3.3-V Operation and Low Static Power Dissipation; (2)Support Mixed-Mode Signal Operation (5-V Input and Output Voltages With 3.3-V VCC); (3)Support Unregulated Battery Operation Down to 2.7 V; (4)Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25℃; (5)ESD Protection Exceeds 2000 V Per MIL-STD-883C, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0); (6)Latch-Up Performance Exceeds 500 mA Per JEDEC Standard JESD-17; (7)Bus-Hold Data Inputs Eliminate the Need for External Pullup Resistors; (8)Support Live Insertion; (9)Package Options Include Plastic Small-Outline (DW), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages, Ceramic Chip Carriers (FK), Ceramic Flat (W) Packages, and Ceramic (J) DIPs.

Diagrams

|

74LV00 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74LV00BQ,115 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) 3.3V QUAD 2-INPUT |

Data Sheet |

|

|

||||||||||||

|

74LV00D |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74LV00D,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74LV00D,118 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74LV00DB,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))