Product Summary

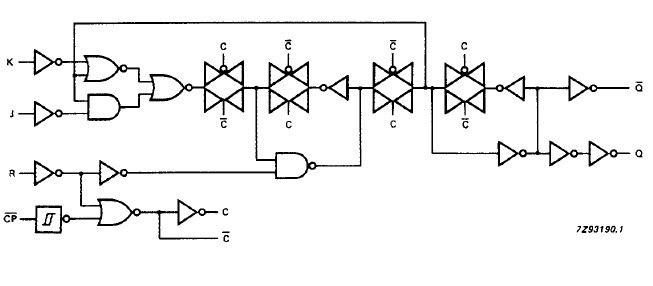

The 74HC107D is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL(LSTTL). It is specified in compliance with JEDEC standard no. 7A. The 74HC107D is dual negative-edge triggered JK-type flip-flops featuring individual J, K, clock (nCP) and reset (nR) inputs; also complementary Q and Q outputs.

Parametrics

74HC107D characteristics: (1)tPHL/ tPLH propagation delay nCP to nQ: Tamb=+25℃: typ=52ns, max=160ns; Tamb=-40 to +85℃: max=200ns; Tamb=-40 to +125℃, max=240ns; VCC=2.0V; (2)tPHL/ tPLH propagation delay nCP to nQ: Tamb=+25℃: typ=52ns, max=160ns; Tamb=-40 to +85℃: max=200ns; Tamb=-40 to +125℃, max=240ns; VCC=2.0V; (3)tPHL/ tPLH propagation delay nR to nQ, nQ: Tamb=+25℃: typ=52ns, max=155ns; Tamb=-40 to +85℃: max=195ns; Tamb=-40 to +125℃, max=235ns; VCC=2.0V; (4)tTHL/ tTLH output transition time: Tamb=+25℃: typ=19ns, max=75ns; Tamb=-40 to +85℃: max=95ns; Tamb=-40 to +125℃, max=110ns; VCC=2.0V.

Features

74HC107D features: (1)Output capability: standard; (2)ICC category: flip-flops.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC107D |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE TRIG |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC107D,652 |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE |

Data Sheet |

|

|

||||||||||||

|

74HC107DB,118 |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE |

Data Sheet |

|

|

||||||||||||

|

74HC107DB,112 |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE |

Data Sheet |

|

|

||||||||||||

|

74HC107D,653 |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE TRIG |

Data Sheet |

|

|

||||||||||||

|

74HC107DB |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE TRIG |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC107DB-T |

NXP Semiconductors |

Flip Flops DUAL J-K W/NEG-EDGE TRIG |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))